Pub手册4.4.3.3,Write Leveling Adjustment(写入时序校准) 的训练过程,主要目的是调整 写入延迟(Write Latency, WL),确保 写操作 和 数据采样 的时序一致,避免由于时序偏差导致的写入错误。

1. 背景:写时序校准(Write Leveling)

在之前的 Write Leveling(写时序校准) 训练阶段,系统已经将 时钟(CK) 边缘和 数据采样时钟(DQS) 边缘对齐了,但由于信号的延迟差异,写入时的时序(Write Latency (WL))可能仍然不完全满足要求。Write Leveling Adjustment 的任务就是通过进一步调整时序,确保写入操作能够准确地同步,避免写入延迟过长或过短。

2. 调整的方式:增量调整

在 Write Leveling Adjustment 阶段,时序调整的方式非常精确:

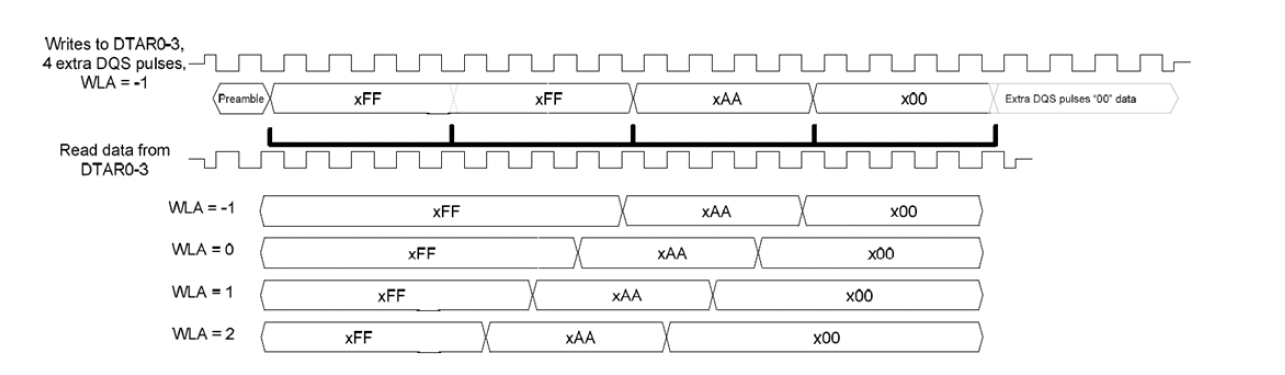

- 时延调整:此过程中的延迟调整是 ½ 个 tCK 周期的增量或减量,意味着每次调整时,延迟只会变化一个小的单位,确保非常精确的时序控制。

- 减少写入延迟:通过在 命令路径 上加入延迟,而 数据路径 保持不变。

- 增加写入延迟:通过在 数据路径 上加入延迟,而 命令路径 保持不变。

3. 训练过程:写操作(WR)与读操作(RD)的交替

- 写操作:为了正确校准时序,系统会发出一系列的 连续写操作(WR Transactions),并且这些写操作使用一个特定的 数据模式,以帮助计算出实际的写入延迟。为了确保写入数据被正确地捕获,写操作包含了一个 扩展后的 DQS 后序脉冲序列,特别是当命令信号的延迟较大时。

- 读操作:在写操作之后,会进行 读操作(RD Transactions),读取刚刚写入的地址,检查数据是否正确地写入。这样可以验证写操作的结果。

4. 数据分析:计算写入延迟

- 读数据之后,系统会分析每一位的数据,特别是在每条数据通道(lane)上逐位分析。通过计算每一位的 1 和 0 的个数,可以推测出写入延迟的正确调整值。

- 如果某些位在上升沿和下降沿的数据不一致(例如 01 和 10),系统会认为这些位的 数据眼(Data Eye) 不可靠,因此会把这些位的数据从校准过程中排除。

- 只有那些在上升沿和下降沿都返回相同值的位才会被用于计算,这些位被认为是 数据眼良好 的,因此可以用于可靠的数据校验。

- 如果 所有位都不一致 或者 数据眼不良,系统就会 丢弃这些比特 并标记为警告。如果无法正确计算 WL 调整值,算法会失败并发出错误信号。

5. 训练结果的验证

- 在 WL 调整值计算完毕之后,会再次发出一组新的写操作和读操作,以验证调整结果是否有效。如果没有错误发生,训练就被视为成功。

- 如果在这一步出现问题,系统会根据 PGSR0.WLAERR 和 DXnRSR3.WLAERR 错误标志,指出出错的通道(rank)和数据通道(lane)。

6. 训练方式

- 单通道模式:每次只训练一个 rank(内存通道),确保每个通道都经过独立训练。

- 双通道共享 AC 模式:在这种模式下,两个 rank 会同时进行训练,确保所有数据通道在同一时间被训练。

本文作者:

ICXNM-ZLin

本文链接: https://talent-tudou.github.io/2024/11/19/DDR/Data Training-Write Leveling Adjustment/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!

本文链接: https://talent-tudou.github.io/2024/11/19/DDR/Data Training-Write Leveling Adjustment/

版权声明: 本作品采用 CC BY-NC-SA 4.0 进行许可。转载请注明出处!